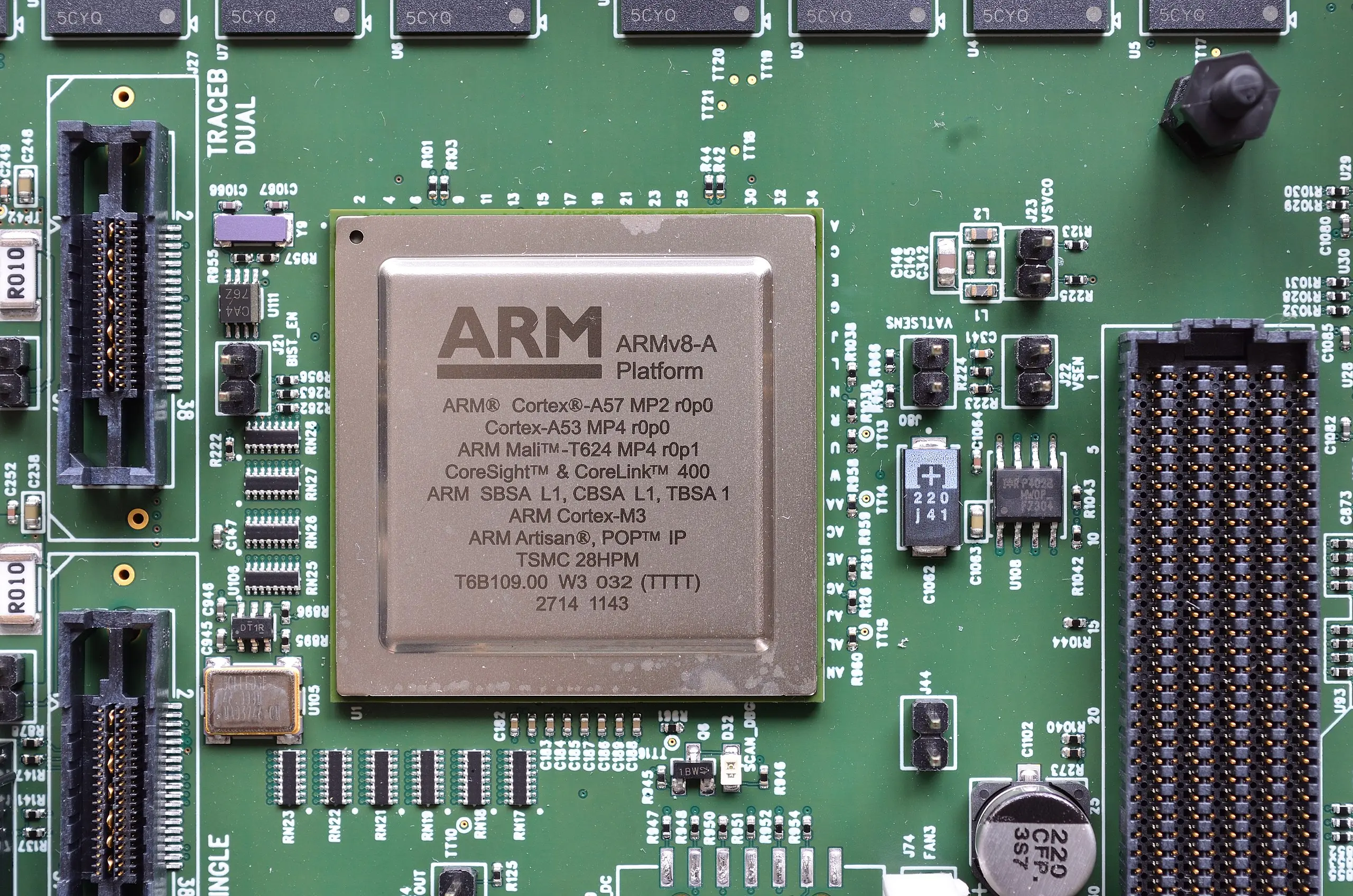

ARM中断及异常

中断和异常

基本概念

中断是主机与外设进行数据通信的重要机制,它负责处理处理器外部的事件;异常实质上也是一种中断,只不过它主要负责处理处理器内部事件。计算机通常是用中断来处理外中断和内部异常,因此在 ARM 技术中,将二者统称为异常。

中断当处理器遇有外部设备发生 “紧急事件” 需要它来处理时,它就必须停下 “手头上的工作” 先去处理这个 “紧急事件”。处理器的这种工作过程,或者这种工作状态就叫做中断。

中断请求当外部设备有紧急事件需要处理器进行处理时,外部设备必须向处理器发送一个 电信号(脉冲或电平) 来表示有事件需要处理器来处理。这个信号叫做 中断请求信号 ,或称 中断请求。

中断源发出中断请求信号的外部设备或事件就叫做中断源。

异常由内部事件引起的中断叫做异常。

中断向量和中断向量表

为了与普通子程序的首地址进行区分,中断服务程序的首地址(入口地址)通常被叫做中断向量,或中断矢量。以后还会看到,凡是能直接或间接指向中断服务程序的都叫中断向量。

在处理器收到中断请求之后,它们都需要获得中断服务程序首地址——中断向量。

所有的中断向量都按一定规律存放在一个固定的存储区域,这个集中存放了中断向量或与中断向量相关信息的存储区域就叫做中断向量表。

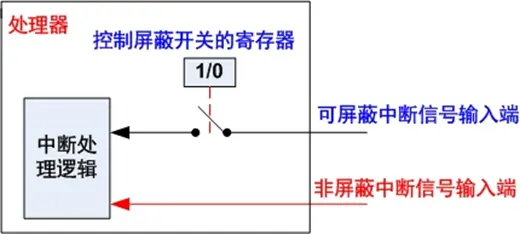

中断请求信号的屏蔽

可屏蔽中断 人们把带有开关,能阻止中断请求的中断输入端叫做可屏蔽中断信号输入端。这类中断叫可屏蔽中断。

非屏蔽中断 人们把不带开关,不能阻止中断请求的中断输入端叫做非屏蔽中断信号输入端。这类中断叫非屏蔽中断。

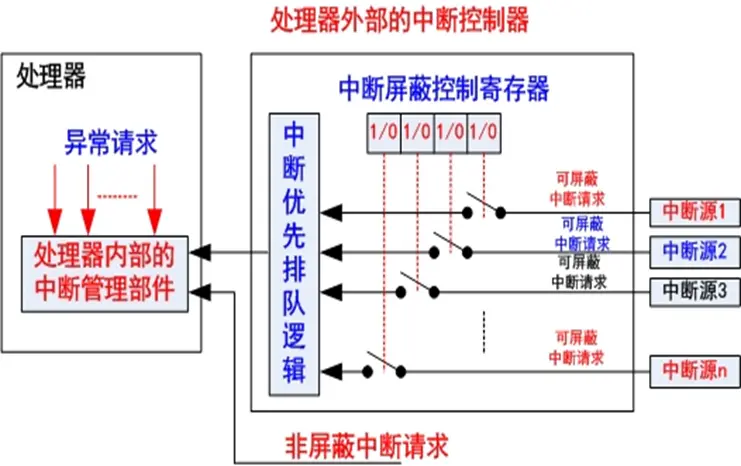

为了对处理器可以接收中断源的数目进行扩充及对中断进行必要的管理,在中断源和处理器之间还配有如下图所示的中断控制器

中断优先级及中断嵌套

处理器通常只有一个可屏蔽中断请求输入端。对于具有 多个中断源的系统来说,当有两个或两个以上中断源同时发生中断请求时就会出现所谓的竞争。

竞争可以通过优先级的方法来处理,具体实现方法有两种:硬件实现方法和软件实现方法。

ARM 异常响应

处理器响应中断的条件

- 处理器程序状态寄存器的中断屏蔽标志处于非屏蔽状态

- 没有更高级的中断请求正在响应或正在发出、正挂起;

- 处理器在现行指令执行结束后

中断的处理过程

- 当有中断请求发生且满足上述条件时,计算机系统就会响应中断请求,并自动将被中断程序的下一条指令地址(断点地址)保存和关闭中断;接下来便将自中断向量表查询得到的与该中断源对应的中断向量送入 PC,并转去执行中断服务程序。

- 当执行到中断服务程序末尾时,执行中断返回指令或跳转指令,把保存的断点地址送回 PC,以在断点处接续执行被中断的程序。

ARM 的中断(异常)向量表

ARM 的中断向量表内存放的是响应异常和中断的转移指令而不是中断向量地址。

在 ARM 处理器中,当异常发生时,完成当前指令后跳转到相应的异常中断处理程序入口执行异常中断处理。异常处理完毕后返回原来的程序断点继续执行原来的程序。

进入异常

在异常发生后,ARM 内核会作以下工作:

- 在适当的 LR 中保存断点的地址

- 把当前程序状态寄存器(CPSR)中的内容保存到模式私有寄存器 SPSR 中

- 将寄存器 CPSR 中的 MODE 域设置为中断(异常)应进入的运行模式;

- 对 CPSR 的 I 位和 F 位进行相应的设置,以防止再次响应同一个中断请求。

- 强制 PC 从相关的异常向量处取指,即到中断向量表中获取中断向量,转向用户所编写的中断(异常)服务程序。

注:异常总是在 ARM 状态中进行处理。当处理器处于 Thumb 状态时发生了异常,在异常向量地址装入 PC 时,会自动切换到 ARM 状态

异常返回

当异常结束时,异常处理程序必须做如下处理:

- 将 SPSR 的值复制回 CPSR

- 将 LR 中的值减去偏移量后存入 PC,偏移量根据异常的类型而有所不同。

ARM 的中断(异常)

ARM 按事件的紧急程度为每个中断(异常)都定义了一个固定的优先级别。当多个异常同时发生时,一个固定的优先级系统决定它们被处理的顺序:

快速中断请求异常 FIQ

有些嵌入式系统的应用对实时性要求比较高,需要足够快的中断响应速度,比如数据转移或通道处理。ARM 在设计上充分地考虑了嵌入式系统的这一特点,在 IRQ 异常之外还设计了一种快速中断请求(FIQ)异常,并在硬件结构和资源分配上给予了足够的支持。

为减少延时,ARM 在快中断中采取了 两个措施:

专门为快中断配置了较多的私有寄存器,从而可使中断服务程序有足够的寄存器来使用,而不必与被中断服务程序使用同一组寄存器,这样就免去了因寄存器冲突而必需的保护及恢复现场工作。

ARM 把 FIQ 的中断向量放在了中断(异常)向量表末尾 0X0000001C 处,因此它后面没有其它中断向量,允许用户将中断服务程序直接放在这里。

Others

自行查阅资料